Test and Reliability Aspects in Neuromorphic Computing

Fei Su - Intel Corporation, US

Abstract:

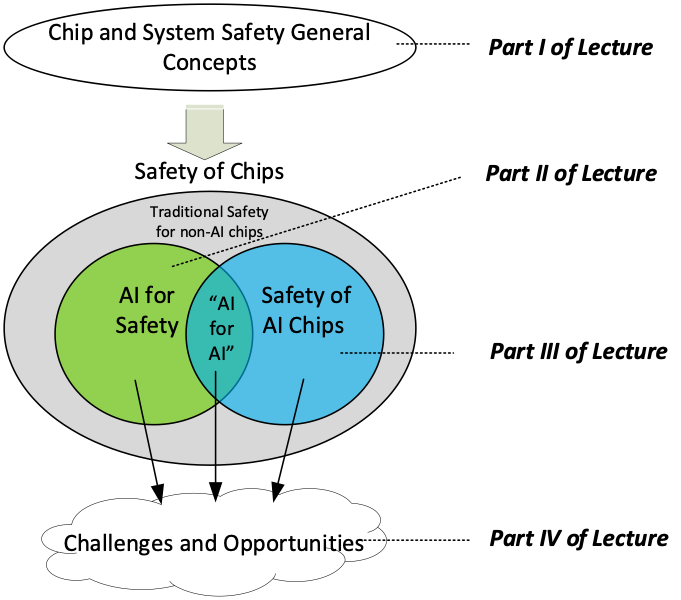

This lecture will cover two distinct but coupled topics: AI application for silicon-based system safety, and Safety of AI chips. Safety of is a critical dependability attribute of silicon-based systems that ensure no harm to people, things or the environment. In recent years there are emerging AI/ML applications to many complicated safety issues (e.g. safety of analog and mixed-signal circuits, freedom-from-interference verification) that traditional approaches are difficult to address. On the hand, more and more AI chips are introduced to accelerate data-intensive AI applications, and they are often integrated in safety-critical autonomous systems (e.g. self-driving vehicles). Safety issues of these AI hardware have aroused great interests. This lecture will provide an introduction of the above topics to students.

Syllabus

Course description: this lecture is intended to provide students with good understanding of key concepts in the safety domain of semiconductor circuits and systems. The lecture will cover two focuses: AI application to safety issues, and Safety assurance of AI chips.

Prerequisites: Basic knowledge of semiconductor chip and system. Also, the student is expected to have basic knowledge of AI models (e.g. DNN, RNN).

Topics: The structure of this lecture is as follows (note it is a preliminary version, subject to update):

- Part I: Semiconductor circuit and system safety overview (1 hour)

- Functional safety (FuSa) overview (ISO 26262, IEC 61508)

- FuSa for semiconductor (ISO 26262.5 and 26262.11)

- Other related safety topics:

- Safety Of The Intended Functionality (SOTIF): ISO 21448

- System-Theoretic Process Analysis (STPA)

- Part II: AI/ML application to safety (1 hour)

- Anomaly detection for safety of analog and mixed-signal circuits

- Causal learning for interference analysis

- Failure prediction for transient and intermittent failures

- Other AI applications for safety assurance

- Part III: Safety of AI chips (1.5 hour)

- AI chip dependability overview

- Design-for-safety approaches for AI chips

- Model level

- Hardware level

- Cross-layer approach

- Part IV: Challenges, trends and opportunities (0.5 hour)

- Challenges on AI application to Safety

- Challenges on safety of AI hardware

- Opportunity

- New standard in development to close gaps

- “AI for AI” virtuous cycle

The following diagram illustrates the topic structure: